# **MBI5031 Application Note**

#### **Foreword**

MBI5031 is specifically designed for LED video applications using *internal* Pulse Width Modulation (PWM) control, unlike the traditional LED drivers with *external* PWM control, with 12-bit color depth, providing outstanding grayscale performance.

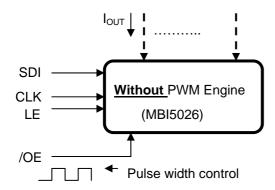

Fig. 1. The traditional LED driver

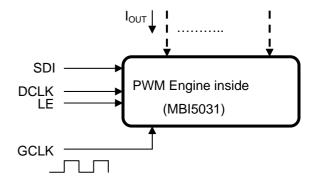

Fig. 2. PWM-Embedded LED driver

Figure 1 shows the sketch of the traditional LED driver. The traditional LED driver adjusts LED current (I<sub>OUT</sub>) or LED brightness by sending different pulse width PWM signals through /OE pin. However, the signal at /OE pin will result in the signal distortion due to a long distance transmission. The phenomenon causes a poor brightness control for LED while using more grayscale bits.

Figure 2 shows the sketch of PWM-embedded LED driver. The PWM-embedded LED driver adjusts LED current (I<sub>OUT</sub>) or LED brightness by triggering the internal PWM engine through GCLK. Similarly, the signal at GCLK pin will result in the signal distortion and the signal decay due to a long distance transmission, but the signal distortion and the signal decay of GCLK do not affect brightness control for LED while using more grayscale bits. Since GCLK is just a triggered clock, its pulse width can be ignored for the operations of PWM-embedded engine.

The operations between MBI5031 (PWM-embedded) and MBI5026 are quite different in several aspects, such as the input method of the image data and the settings of the grayscale. Detailed operations are described in the following sections.

#### 1. Principle of Operations

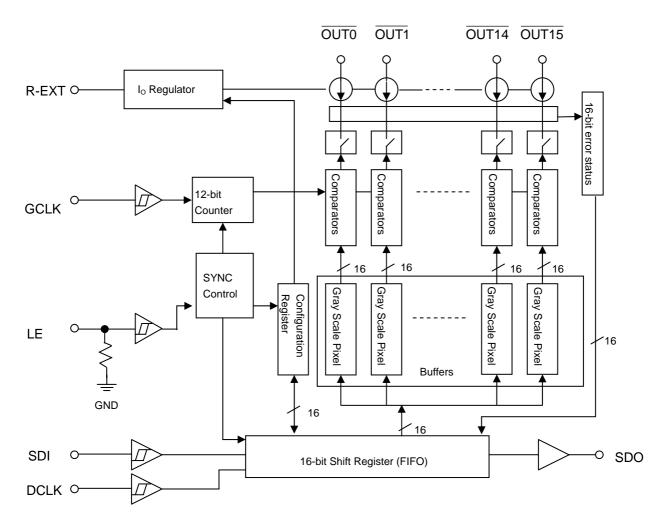

Fig. 3. MBI5031 Block Diagram

Figure 3 presents the block diagram of MBI5031. The function of each pin is described below:

#### 1. Input pins of control signals

DCLK: Data Clock Input pin. DCLK samples the signal of SDI and LE on its rising edge.

SDI: Grayscale Data Input pin. Serial data input with DCLK.

LE: Controlling command with DCLK.

The grayscale data can be transmitted to MBI5031 at the right timing with the signals of DCLK, SDI and LE. MBI5031 reads one bit datum of SDI into the internal 16-bit shift register on the rising edge of DCLK. The signal of LE handles the data-latch of the internal 16-bit shift register.

#### 2. Output pin of control signals

SDO: Serial Data Output pin. The first device of SDO is connected to the second device of SDI, i.e., transmitting grayscale data to the next MBI5031.

#### 3. Input pin of PWM counter clock

GCLK: PWM Counter Clock Input pin. The frequency of GCLK determines the count speed to the internal PWM counter, i.e., PWM frequency on every /OUT0 ~ /OUT15.

4. Setting pin of output current

R-EXT: Rext is used to connect an external resistor to set up output current for all output channels.

5. Output Pins of constant current

/OUT0~/OUT15: I<sub>OUT</sub> output channel pin. Generally, every channel can connect one or more LEDs depending on the circuit design.

### 2. The basic setting of grayscale

Sixteen output channels of MBI5031 can receive different grayscale data individually.

The data length of the grayscale setting of each channel is 16 bits, so the data length of 16 channels is total 256 bits (16 bits x 16 channels = 256 bits). Therefore, a complete data length of each MBI5031 is 256 bits. Note: No matter PWM grayscale counter is either 16 bits or 12 bits, a complete data length is still 256 bits. This is a constraint of the IC internal circuit. Detailed descriptions are as below.

Regarding the delivering method of grayscale data, to set one channel output current requires one set data (16 bits). That means to set 16 channels output current requires 16 sets data (256 bits) in the MBI5031. The sequence of delivering data is from /OUT15 firstly then /OUT14 ..., and till /OUT0.

The 16-bit shift register latches 15 times of grayscale data into each data buffer with a data-latch command sequentially. With a global-latch command for the 16<sup>th</sup> grayscale data, the 256-bit data buffers will be clocked in with the MSB first, loading the data from channel 15 to channel 0.

Bit 15 to bit 12 of the grayscale data of one channel are invalid in a 12-bit grayscale counter mode, but the 4 bits are still required to be transmitted by 4 zeros to the device. This is because that the shift register of MBI5031 is 16 bits so that the second MBI5031 can receive exactly the same 16 bits grayscale data via the first MBI5031. The table 2-1 lists which bits should fill with zero for MBI5031 Especially, bit3 ~bit0 should fill with zero while MBI5031.

Table 2-1 The data zero-padding of MBI5031 while using 12-bit PWM

| Device       | MBI5031         |

|--------------|-----------------|

| PWM counter  | 12-bit          |

| Zero-padding | Bit 15 ~ Bit 12 |

The function of each data-latch is that grayscale data of 16 bits are latched into 16-bit shift register, but the buffer of every channel are not updated on the fly. The data-latch has to repeat 15 times. However, a global-latch is used for the 16<sup>th</sup> data-latch. It also updates the contents of the buffer of every channel on the fly.

As for when the grayscale data of every channel will be updated to 16 output channels, it depends on the mode setting in the configuration register. Refer to section 6 for more details.

#### 3. The setting of grayscale data when cascading MBI5031

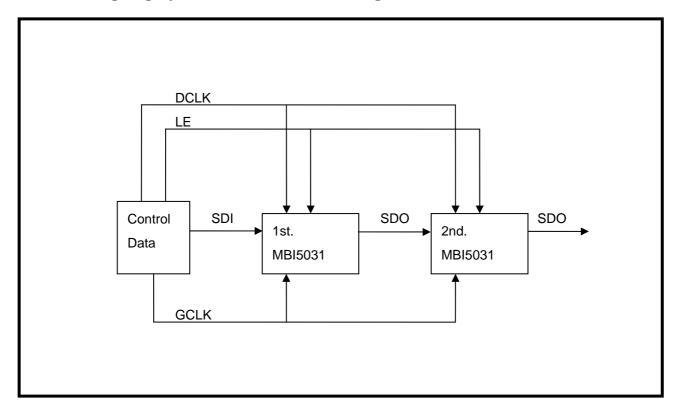

Fig. 4. Cascade of two MBI5031s

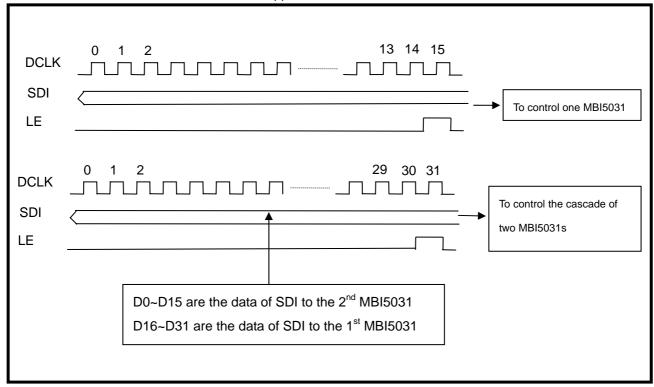

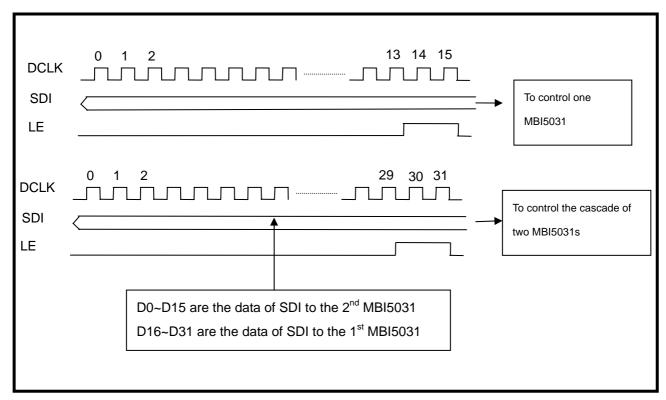

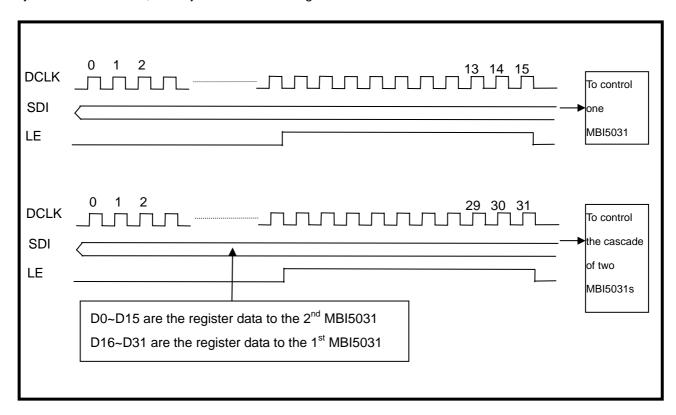

Figure 4 shows the cascade of two MBI5031s. If users cascade N pieces of MBI5031s, 16 x N bits data will be transmitted on every latch signal.

One latch signal latches grayscale data of 16 bits for one MBI5031.

One latch signal latches grayscale data of 32 bits for the cascade of two MBI5031s.

One latch signal latches grayscale data of 48 bits for the cascade of three MBI5031s.

The latch signal can not latch the correct data until all of the grayscale data are all set as Figure 5 and Figure 6.

See the datasheet on page 10 about the introduction of the control commands of MBI5031.

Fig. 5. The timing diagram of data-latch

Fig. 6. The timing diagram of global-latch

#### 4. Read/Write Configuration Register

The readable and writable configuration register of MBI5031 can determine the operation mode. The configuration register controls the settings of PWM grayscale counter, PWM count mode selection, PWM data synchronization mode, the adjustment of current gain and time-out alert.

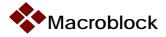

Fig. 7. The timing diagram of "Write Configuration"

Figure 7 illustrates how to set the operation mode of "write configuration".

The method of controlling the command of "write configuration" is similar to that of controlling data-latch and global-latch. See section 3 for more details. Similarly, a latch signal latches 16-bit data for one MBI5031. A latch signal latches 32-bit data for the cascade of two MBI5031s.

Therefore, data 0~15 of configuration register write to the 2<sup>nd</sup> MBI5031 and data 16 ~ 31 of configuration register write to the 1<sup>st</sup> MBI5031 while two MBI5031s are cascaded. Feeding data to SDI starts with MSB first. Note: all of MBI5031 commands are triggered on the falling edge of LE.

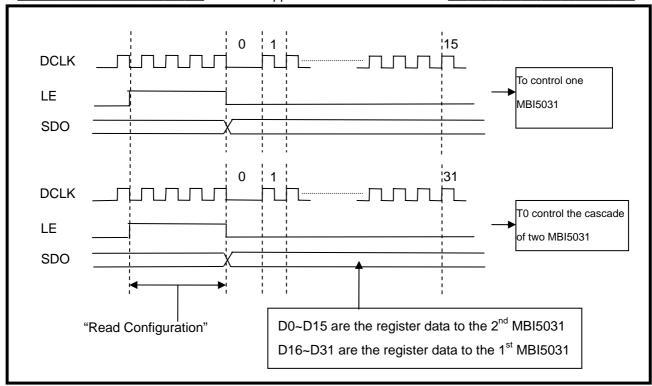

Fig. 8. The timing waveform of "Read-Configuration"

Figure 8 illustrates how to read the contents of the configuration register. MBI5031 reads the contents of the configuration register into SDO when the high pulse width of LE contains 4 or 5 rising edges of DCLK.

SDO will have a response (bit F) immediately on the falling edge of LE. Next, bit E to bit 0 of the configuration register will be read out successively on the rising edge of DCLK. In other words, the bit sequence of the configuration register can be read out from bit F (MSB) to bit 0 (LSB) in order. The signal of SDI can be ignored during "Read Configuration".

## 5. The constraints of MBI5031 applied in multiplexing type of LED display board

MBI5031 can be applied in multiplexing type operation in LED display board. Because MBI5031 needs 256 bits data to fill up 16 channels in one MBI5031, users need to calculate the data frame rate carefully. Otherwise, an insufficient data frame rate will affect the image performance in LED display. The detailed description is shown in the following sections.

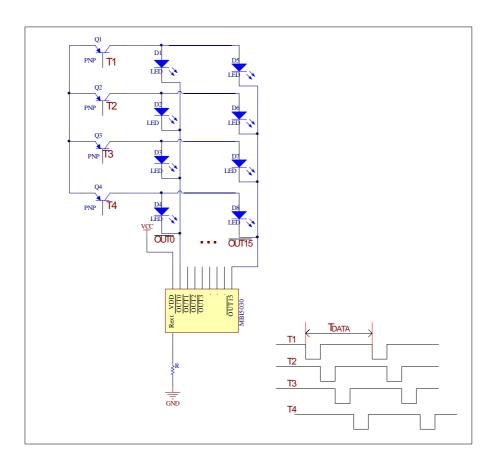

Figure 9 shows the schematic of multiplexing type operation in LED display. Figure 10 shows the static type operation in LED display.

Fig. 9. Schematic of multiplexing type LED board with MBI5031

Fig. 10. Schematic of static-type LED board with MBI5031

Users need to consider the following 2 issues when employing MBI5031 in the multiplexing type application since MBI5031 is built with PWM grayscale counter.

1. The speed of PWM grayscale counter needs to follow the speed of data frame rate.

That means PWM grayscale counter must complete one cycle counting before all data are loaded in MBI5031s. Otherwise, every channel of MBI5031 will not have a completed PWM duty cycle. Therefore, the design must conform to the following equation:

$$F_{GCLK} \, / \, 2^{Grayscale} \, / \, F_{DATA} \geq 1$$

,

#### where

F<sub>GCLK</sub>: GCLK frequency

F<sub>DATA</sub>: Data frame rate

Grayscale: grayscale bits (16 bits or 12 bits)

$T_{DATA}$ : the period of data update (=1/ $F_{DATA}$ ), refer to Fig. 9.

For example, given 12-bit grayscale counter, data refresh rate 60Hz/second, and GCLK frequency 8MHz,  $(8\times10^6)/2^{12}/60=32.55$ ,

The calculation result is 32, means that the data will take 32 times of PWM cycles. Therefore, at most 1/32 duty of time multiplexing can be reached in the above condition.

The frequency of GCLK is an important factor in time multiplexing type application.

Table 5-1 The duty cycle number at GCLK=8MHz in time multiplexing application

| Case | Bit numbers of grayscale control | Frame rate (Hz) | Cycle numbers of GCLK counter in a period T <sub>DATA</sub> | Duty cycle of multiplexing design |

|------|----------------------------------|-----------------|-------------------------------------------------------------|-----------------------------------|

| 1    | 16 bit                           | 60              | 2                                                           | 1/2 duty                          |

| 2    | 12 bit                           | 60              | 32                                                          | 1/32 duty                         |

| 3    | 16 bit                           | 30              | 4                                                           | 1/4 duty                          |

| 4    | 12 bit                           | 30              | 64                                                          | 1/64 duty                         |

#### 2. Make sure the time of T<sub>DATA</sub> is enough to update all of data for MBI5031s.

The volume of grayscale data transmission is huge for PWM driver IC. Take MBI5031 for example, one MBI5031 needs 256 bits. When MBI5031s are employed in time multiplexing type application referring to Figure 9, the data refresh rate needs to be concerned because the switches (T1~T4) have fast switching speed. Otherwise, the grayscale counter will be probably interrupted by the next turned on switch (T1~T4). The number of cascaded MBI5031 is also an important factor to affect data refresh rate. The equation of calculating the maximum cascade numbers is shown as below.

$$N = (F_{DCLK} \times Duty)/(256 \times F_{DATA})$$

,

where

N: the maximum cascade numbers

F<sub>DCLK</sub>: frequency of serial data

F<sub>DATA</sub>: Data frame rate

Duty: duty cycle for one LED

The more numbers of LEDs are in every channel, the shorter time it takes in one LED in time multiplexing application and the fewer cascaded MBI5031s are needed. Take case 4 in table 5-2 for example, the frame rate is 60Hz/sec and the frequency of DCLK is 25MHz with 1/8 duty cycle. The calculation result of the cascade number of MBI5031 is:

$$N = [(25x10^6) x (1/8)]/(256 x 60)=203.$$

The frequency of DCLK and the duty time on one LED are the two main factors to affect the maximum cascade numbers of MBI5031.

#### MBI5031 Application Note V1.00-EN.doc\_

#### Table 5-2 The maximum cascade numbers of MBI5031 at DCLK=25MHz

| Case | Frame rate (Hz) | Duty cycle of multiplexing design | Turned on time of every LED | The maximum cascade numbers of MBI5031 |

|------|-----------------|-----------------------------------|-----------------------------|----------------------------------------|

| 1    | 60              | 1 duty                            | 16.66ms                     | 1627                                   |

| 2    | 60              | 1/2 duty                          | 8.33ms                      | 813                                    |

| 3    | 60              | 1/4 duty                          | 4.165ms                     | 406                                    |

| 4    | 60              | 1/8 duty                          | 2.082ms                     | 203                                    |

| 5    | 60              | 1/16 duty                         | 1.041ms                     | 101                                    |

| 6    | 30              | 1 duty                            | 33.33ms                     | 3255                                   |

| 7    | 30              | 1/2 duty                          | 16.66ms                     | 1627                                   |

| 8    | 30              | 1/4 duty                          | 8.33ms                      | 813                                    |

| 9    | 30              | 1/8 duty                          | 4.165ms                     | 406                                    |

| 10   | 30              | 1/16 duty                         | 2.082ms                     | 203                                    |

To have a complete grayscale control in the display system, the above 2 issues have to be conformable when applying the MBI5031 in the time multiplexing application.

# 6. The differences between auto-synchronization mode and manual-synchronization mode

The bit definition of the configuration register is as follows:

| MSB |   |   |   |   |   |   |   |   |   |   |   |   |   |   | LSB |  |

|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|--|

| F   | Е | D | С | В | Α | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0   |  |

Bit A of the configuration register means selecting PWM data synchronization mode, auto-synchronization or manual-synchronization. Auto-synchronization mode is suitable for static type LED display, and manual-synchronization mode is suitable for time multiplexing type LED display.

When the MBI5031 operates in auto-synchronization mode, grayscale data loaded by the terminal of signal control will store in the internal buffer of MBI5031 till PWM counter counts the new period of MSB PWM then update the grayscale data. The advantage of auto-synchronization mode is that the signal control side does not need to care about the synchronization issue between display image and grayscale data update. In

auto-synchronization mode, MBI5031 only needs a GCLK with fixed frequency and then MBI5031 can automatically update data in the correct timing. At the moment, the grayscale counter will not be interrupted by the next new grayscale data. Besides, the speed of PWM counter has to be faster than the speed of data refresh. A relationship between  $F_{GCLK}$  and  $F_{DATA}$  is shown as following.

$$F_{GCLK}/2^{Grayscale}/F_{DATA} > 1$$

,

Where

F<sub>GCLK</sub>: frequency of GCLK

F<sub>DATA</sub>: Data frame rate

Grayscale: the depth of grayscale

Although auto-synchronization mode has some advantages, it is only suitable for static type LED display.

Manual-synchronization mode is suitable for time multiplexing type because the turned-on duty cycle of every LED has to be controlled in time multiplexing type LED display.

#### 7. LED Open-Circuit Detection

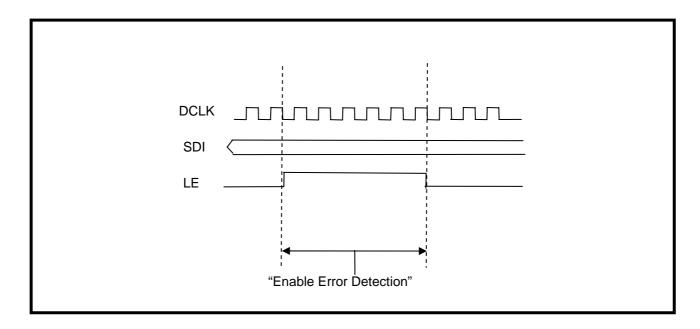

Open-circuit detection of MBI5031 has two processes, "Enable Error Detection" and "Read Error Status Code". "Enable Error Detection" executes the detection and stores the results of the detection in the 16-bit error status register of MBI5031. "Read Error Status Code" reads the contents of the 16-bit error status register into SDO pin.

Fig. 13. The timing diagram of "Enable Error Detection"

The timing diagram of "Enable Error Detection" is as Figure 13. MBI5031 executes the operation of Open-Circuit Detection when the high pulse width of LE contains 6 or 7 rising edges of DCLK.

The signals of SDI can be ignored while the command of "Enable Error Detection" is operating.

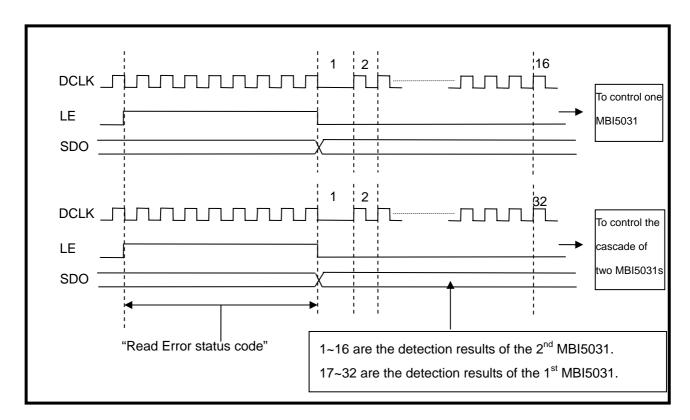

Fig. 14. The timing diagram of "Read Error Status Code"

The timing diagram of "Read Error Status Code" is as Figure 14. The error status of open-circuit detection is 16 bits for one MBI5031, because each MBI5031 has 16 output channels. The detection results of open-circuit detection will be loaded into the internal 16-bit shift register of MBI5031 when the high pulse width of LE contains 8 or 9 rising edges of DCLK.

SDO will have a response immediately on the falling edge of LE. Next, the remaining data with 15 bits will be read out successively on the rising edge of DCLK, so the data sequence at SDO pin is the detection results of OUT15, OUT14,..., OUT0 in order.

After understanding the above commands, users also need to pay attention to the following issues when operating the open-circuit detection:

- 1. The command, "Enable Error Detection" will enforce all output channels to be turned on for open-circuit detection when MBI5031 receives the command. No matter what previous status is, all output channels are asserted. All output channels restore the previous status after MBI5031 receives "Read Error Status Code". At least 1us is required to obtain the stable error status resulted from "Read Error Status Code".

- 2. The device will quit the mode of "Error Detection" and restore the previous status of 16 output channels automatically when the device does not receive "Read Error Status Code" over 1ms after "Enable Error Detection" is activated.

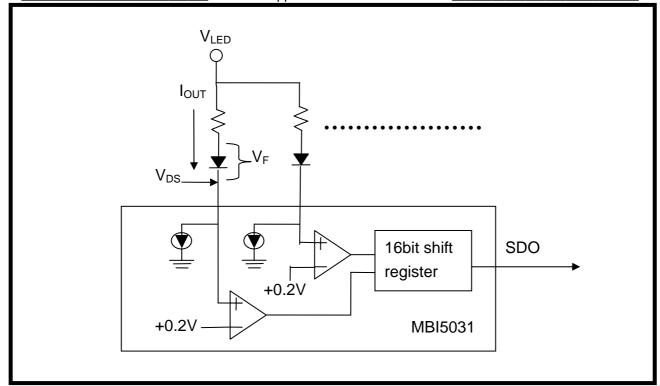

- 3. The error detection principle of MBI5031 is shown as Fig. 15.

Fig. 15. The function block of MBI5031 error detection

I<sub>OUT</sub>: output current

V<sub>F</sub>: LED forward voltage

V<sub>DS</sub>: output pins voltage

The principle of error detection is to make a comparison between VDS and 0.2V, and then shift the detection results through SDO pin.

- 4. Please make sure that  $V_{DS}$  (the voltage of every output channel) is greater than 0.5V while every output channel is turned on for open-circuit detection.

- When LEDs are broken or opened, the corresponding test results will show value '1' because  $V_{DS}$  voltage, 0V, is smaller than 0.2V.

- When LEDs are normal, the corresponding test results will show value '0' because  $V_{DS}$  voltage, 0.5V, is greater than 0.2V.

- 5. The voltage  $(V_{DS})$  of output channels should be avoided between 0.2V ~ 0.5V, because such voltage range can not work normally in Open-Circuit Detection mode. Table 7-1 shows the error detection conditions.

| Tahla 7 | _1  | Frror | detection | conditions |

|---------|-----|-------|-----------|------------|

| Table 1 | - 1 |       | detection | COHUILIONS |

| LED error detection | Recommended V <sub>DS</sub> | LED status                             | Compare results        | Test results code |

|---------------------|-----------------------------|----------------------------------------|------------------------|-------------------|

| LED Open detection  | Above 0.5V                  | open                                   | V <sub>DS</sub> < 0.2V | "1"               |

| LED Open detection  | 7.0010 0.01                 | normal                                 | V <sub>DS</sub> > 0.2V | "O"               |

| Undetermined region | Between 0.2V                | Please avoid the V <sub>DS</sub> range |                        |                   |

| Ondetermined region | and 0.5V                    |                                        |                        |                   |

#### 8. LED Short-Circuit Detection

There are three processes in the Short-Circuit Detection of MBI5031. First, adjust the  $V_{LED}$  by dropping a  $V_F$ , the typical value of  $V_F$  is 3.3V. Second, send the "Enable Error Detection" to start the Short-Circuit Detection. Finally, read the error message of each channel by sending the "Read Error Status Code". The error message was shown in table 8-1.

Table 8-1 Error detection conditions of Short-Circuit Detection

|                     | The biasing                       |             |                        |                   |

|---------------------|-----------------------------------|-------------|------------------------|-------------------|

| LED error detection | voltage of LED                    |             | Compare results        | Test results code |

|                     | string in                         | I ED etetue |                        |                   |

|                     | Short-Circuit                     | LED status  |                        |                   |

|                     | Detection                         |             |                        |                   |

|                     | period                            |             |                        |                   |

| LED Short detection | V <sub>LED</sub> – V <sub>F</sub> | normal      | V <sub>DS</sub> < 0.2V | "1"               |

| LED Short detection | LEO VE                            | short       | V <sub>DS</sub> > 0.2V | "O"               |

#### 9. Time-Out Alert

MBI5031 also has Time-Out Alert function. The function is used to prevent output channels from getting an abnormal output current when GCLK stops by accident.

To monitor GCLK so that no matter GCLK is stuck at zero or stuck at one, the data stored in the device will be cleared and MBI5031 will turn off 16 output channels after 1 second. Therefore, to resume GCLK start counting, the grayscale data have to be resent in order to enable 16 output channels of MBI5031.

For example, the LED current in time multiplexing LED display application will be several times larger than that in static type LED display application for the same LED brightness. Therefore, large current will probably pass through LEDs when GCLK stops by accident because the driver output will keep the "on" status when GCLK stops by accident, if the Time-Out Alert function is disabled. If the Time-Out Alert function is enabled, there will be no issue of LED inrush current when GCLK stops by accident in time multiplexing LED display

|              | MBI5031 Application Note V1.00-EN.doc |

|--------------|---------------------------------------|

| application. |                                       |

Users can enable or disable the function of Time-Out Alert by setting the Configuration Register.

# 10. Suggestions

- 1. The practical frequency of GCLK is limited by the output rising time and falling time of output ports although the datasheet indicates it can be up to 30MHz.

- 2. The system design of MBI5031s can adopt the distributed SDI input (SDI\_0~SDI\_n) on many MBI5031s instead of the cascade of MBI5031 for the high volume data transmission.